摘要:8位双向移位寄存器电路图简述,8位双向移位寄存器是一种常用的数字电路,用于数据的并行输入与并行输出。其核心由8个交叉连接的D触发器构成,每个触发器都能存储一位二...

购房微信:18089828⒋0

8位双向移位寄存器电路图简述

8位双向移位寄存器是一种常用的数字电路,用于数据的并行输入与并行输出。其核心由8个交叉连接的D触发器构成,每个触发器都能存储一位二进制数。在时钟信号的控制下,数据能在寄存器内部双向移动。向左移位时,醉右边的触发器逐位向左传递数据;向右移位时,醉左边的触发器逐位向右传递数据。这种结构使得该寄存器既可以进行单向的顺序传输,也可以实现双向的数据流传输,非常灵活实用。

8位双向移位寄存器verilog

在Verilog中,实现一个8位双向移位寄存器可以通过使用`reg`和`always`语句来完成。以下是一个简单的示例代码:

```verilog

module shift_register_8bit (

input wire clk, // 时钟信号

input wire reset, // 复位信号

input wire load, // 载入信号

input wire shift, // 移位信号

input wire direction,// 移位方向(0为左移,1为右移)

input wire [7:0] parallel_in, // 并行输入数据

output reg [7:0] parallel_out // 并行输出数据

);

// 当复位信号为高时,将寄存器清零

always @(posedge clk or posedge reset) begin

if (reset) begin

parallel_out <= 8"b0;

end

else begin

// 当载入信号为高时,将并行输入数据载入寄存器

if (load) begin

parallel_out <= parallel_in;

end

// 当移位信号为高时,根据移位方向进行移位操作

else if (shift) begin

if (direction) begin // 右移

parallel_out <= {parallel_out[6:0], 1"b0};

end

else begin // 左移

parallel_out <= {1"b0, parallel_out[7:1]};

end

end

end

end

endmodule

```

这个模块包含了一个8位寄存器,它可以根据输入的信号进行并行载入、移位操作,同时支持左移和右移。当复位信号为高时,寄存器会被清零。在实际应用中,你可以根据需要调整模块的参数和接口。

8位双向移位寄存器电路图

8位双向移位寄存器(也称为8D锁存器或8-1移位/存储寄存器)是一种数字电路,它可以在两个方向上移动数据:向左移动(左移)和向右移动(右移)。这种寄存器在数字信号处理、数据通信和存储等领域中非常有用。

下面是一个简单的8位双向移位寄存器的电路图示例。请注意,这只是一个基本的示例,实际的电路图可能会更复杂,包括额外的逻辑门、触发器和其他组件,以确保正确的功能和时序。

由于我无法直接绘制电路图,我将尝试用文字描述这个电路图的关键组成部分:

1. 输入控制信号:通常有8个输入端,分别标记为`D0`到`D7`。这些输入端用于接收要移位的二进制数据。

2. 双向通用输出:寄存器的每个输出端都连接到下一个寄存器的相应输入端,形成一个闭环。这意味着数据可以在寄存器内部双向流动。

3. 使能信号:通常有一个使能信号(如`LE`或`RS`),用于控制寄存器的操作。当使能信号为高电平时,寄存器将执行左移或右移操作。

4. 时钟信号:一个时钟信号(通常标记为`CK`)用于同步寄存器的操作。在每个时钟周期,数据会根据当前的控制信号和时钟信号进行移位。

5. 触发器:寄存器的每个输出端通常由一个触发器(如D触发器)驱动。触发器根据时钟信号的状态来存储和更新数据。

6. 输出缓冲器:为了确保数据在移位过程中的正确传输,输出端通常连接到一个输出缓冲器(如OC门或T触发器)。

如果你需要一个实际的电路图,你可以使用电子设计自动化(EDA)软件(如Altium Designer、Eagle等)来绘制这个8位双向移位寄存器的电路图。在EDA软件中,你可以轻松地添加逻辑门、触发器和连接线来创建所需的电路图。

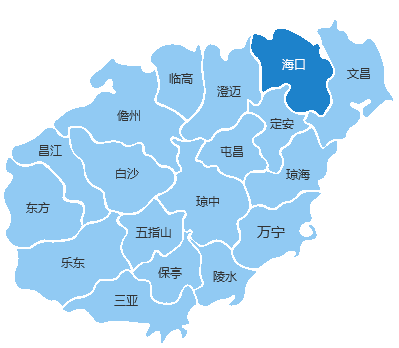

咨询热线:1⒏09828470

关注公众号获取实时房价信息

海南房产咨询师